Operazioni logiche a parola

| Elemento | Descrizione |

|

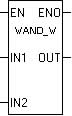

Combinazione AND di word Ingressi/uscite: EN ingresso di abilitazione (E, A, M, DBX, T, Z) ENO uscita di abilitazione (E, A, M, DBX, T, Z) IN1 primo valore dell’operazione logica (EW, AW, MW, DBW, costante 16 bit) IN2 secondo valore dell’operazione logica (EW, AW, MW, DBW, costante 16 bit) OUT risultato dell’operazione logica (EW, AW, MW, DBW) I valori delle variabili a 16 bit specificate agli ingressi IN1 e IN2 vengono combinati bit a bit in AND. Il risultato è disponibile all’uscita OUT. L’operazione viene eseguita solo su stato 1 dell’ingresso di abilitazione EN. L’uscita ENO ha lo stesso valore dell’ingresso IN. Se il risultato dell’operazione logica è diverso da 0, il bit A1 della parola di stato viene settato; se il risultato dell’operazione logica è uguale a 0, il bit A1 della parola di stato viene resettato. |

|

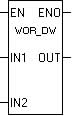

Combinazione OR di word Ingressi/uscite: EN ingresso di abilitazione (E, A, M, DBX, T, Z) ENO uscita di abilitazione (E, A, M, DBX, T, Z) IN1 primo valore dell’operazione logica (EW, AW, MW, DBW, costante 16 bit) IN2 secondo valore dell’operazione logica (EW, AW, MW, DBW, costante 16 bit) OUT risultato dell’operazione logica (EW, AW, MW, DBW) I valori delle variabili a 16 bit specificate agli ingressi IN1 e IN2 vengono combinati bit a bit in OR. Il risultato è disponibile all’uscita OUT. L’operazione viene eseguita solo su stato 1 dell’ingresso di abilitazione EN. L’uscita ENO ha lo stesso valore dell’ingresso IN. Se il risultato dell’operazione logica è diverso da 0, il bit A1 della parola di stato viene settato; se il risultato dell’operazione logica è uguale a 0, il bit A1 della parola di stato viene resettato. |

|

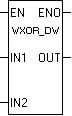

Combinazione OR esclusivo di word Ingressi/uscite: EN ingresso di abilitazione (E, A, M, DBX, T, Z) ENO uscita di abilitazione (E, A, M, DBX, T, Z) IN1 primo valore dell’operazione logica (EW, AW, MW, DBW, costante 16 bit) IN2 secondo valore dell’operazione logica (EW, AW, MW, DBW, costante 16 bit) OUT risultato dell’operazione logica (EW, AW, MW, DBW) I valori delle variabili a 16 bit specificate agli ingressi IN1 e IN2 vengono combinati bit a bit in OR esclusivo. Il risultato è disponibile all’uscita OUT. L’operazione viene eseguita solo su stato 1 dell’ingresso di abilitazione EN. L’uscita ENO ha lo stesso valore dell’ingresso IN. Se il risultato dell’operazione logica è diverso da 0, il bit A1 della parola di stato viene settato; se il risultato dell’operazione logica è uguale a 0, il bit A1 della parola di stato viene resettato. |

|

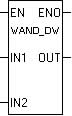

Combinazione AND di doppia word Ingressi/uscite: EN ingresso di abilitazione (E, A, M, DBX, T, Z) ENO uscita di abilitazione (E, A, M, DBX, T, Z) IN1 primo valore dell’operazione logica (ED, AD, MD, DBD, costante 32 bit) IN2 secondo valore dell’operazione logica (ED, AD, MD, DBD, costante 32 bit) OUT risultato dell’operazione logica (ED, AD, MD, DBD) I valori delle variabili a 32 bit specificate agli ingressi IN1 e IN2 vengono combinati bit a bit in AND. Il risultato è disponibile all’uscita OUT. L’operazione viene eseguita solo su stato 1 dell’ingresso di abilitazione EN. L’uscita ENO ha lo stesso valore dell’ingresso IN. Se il risultato dell’operazione logica è diverso da 0, il bit A1 della parola di stato viene settato; se il risultato dell’operazione logica è uguale a 0, il bit A1 della parola di stato viene resettato. |

|

Combinazione OR di doppia word Ingressi/uscite: EN ingresso di abilitazione (E, A, M, DBX, T, Z) ENO uscita di abilitazione (E, A, M, DBX, T, Z) IN1 primo valore dell’operazione logica (ED, AD, MD, DBD, costante 32 bit) IN2 secondo valore dell’operazione logica (ED, AD, MD, DBD, costante 32 bit) OUT risultato dell’operazione logica (ED, AD, MD, DBD) I valori delle variabili a 32 bit specificate agli ingressi IN1 e IN2 vengono combinati bit a bit in OR. Il risultato è disponibile all’uscita OUT. L’operazione viene eseguita solo su stato 1 dell’ingresso di abilitazione EN. L’uscita ENO ha lo stesso valore dell’ingresso IN. Se il risultato dell’operazione logica è diverso da 0, il bit A1 della parola di stato viene settato; se il risultato dell’operazione logica è uguale a 0, il bit A1 della parola di stato viene resettato. |

|

Combinazione OR esclusivo di doppia word Ingressi/uscite: EN ingresso di abilitazione (E, A, M, DBX, T, Z) ENO uscita di abilitazione (E, A, M, DBX, T, Z) IN1 primo valore dell’operazione logica (ED, AD, MD, DBD, costante 32 bit) IN2 secondo valore dell’operazione logica (ED, AD, MD, DBD, costante 32 bit) OUT risultato dell’operazione logica (ED, AD, MD, DBD) I valori delle variabili a 32 bit specificate agli ingressi IN1 e IN2 vengono combinati bit a bit in OR esclusivo. Il risultato è disponibile all’uscita OUT. L’operazione viene eseguita solo su stato 1 dell’ingresso di abilitazione EN. L’uscita ENO ha lo stesso valore dell’ingresso IN. Se il risultato dell’operazione logica è diverso da 0, il bit A1 della parola di stato viene settato; se il risultato dell’operazione logica è uguale a 0, il bit A1 della parola di stato viene resettato. |

D5 Creation

D5 Creation